Trạng thái Trở kháng cao

Thứ ba - 22/01/2013 08:27

Trạng thái trở kháng cao Z

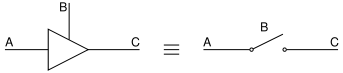

Trạng thái hở mạch này được gọi là Trạng thái Trở kháng cao Z = ∞ và được gọi là Trạng thái Logic thứ 3. Các mạch Logic nào có thêm Trạng thái Trở kháng cao thì được gọi là Mạch Logic 3 Trạng thái.

Trạng thái hở mạch này được gọi là Trạng thái Trở kháng cao Z = ∞ và được gọi là Trạng thái Logic thứ 3. Các mạch Logic nào có thêm Trạng thái Trở kháng cao thì được gọi là Mạch Logic 3 Trạng thái.Chú ý: Trạng thái thứ 3 (Trở kháng cao) chỉ có tác dụng đối với Ngõ ra, không có tác dụng đối với Ngõ vào.

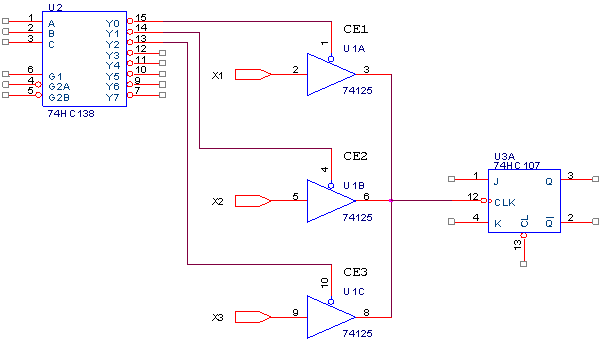

Mạch trên đây mô tả cho thấy có 3 Ngõ ra sử dụng ghép chung nhau gồm U1A, U1B và U1C. Vì vậy, nếu cả 3 Mạch Logic này cùng hoạt động đồng thời thì sẽ có trường hợp ít nhất có 1 Mạch có Trạng thái Logic nghịch đảo so với 2 Mạch Logic kia tức là có 2 Mạch Logic có Ngõ ra ở mức cao (bằng H) và 1 Mạch lại có Ngõ ra ở mức thấp (bằng L) thì dễ thấy rằng Ngõ ra có mức thấp có nguy cơ trở thành Tải của 2 Ngõ ra có mức cao vì vậy 3 Mạch trên phải hoạt động tuần tự sao cho ở mỗi thời điểm chỉ có 1 trong 3 Mạch Logic hoạt động mà thôi, 2 Mạch Logic còn lại phải ở trạng thái Trở kháng cao.

Quá trình hoạt động tuần tự của 3 Mạch Logic nói trên được thực hiện bằng cách sử dụng IC Giải mã U2 để tạo ra các lệnh CE1, CE2 và CE3 tuần tự nhau.

Chú ý: Nếu cả 3 Ngõ ra của IC U1 đều ở trạng thái trở kháng cao thì Ngõ vào của IC U3A là chân CLK bị hở mạch và ở trạng thái đầu vào bị hở mạch sẽ được coi là trạng thái mức cao.

Tác giả bài viết: Dr Trần Phúc Ánh

Lưu ý: Các bài viết trên in lại các trang web hoặc các nguồn phương tiện truyền thông khác không xác định nguồn http://tri-heros.net là vi phạm bản quyền

Xem phản hồi

Xem phản hồi Gửi phản hồi

Gửi phản hồi