Mạch NAND

Thứ tư - 23/01/2013 03:10

Các trạng thái Logic của Mạch NAND

Mạch Và Đảo (NAND)

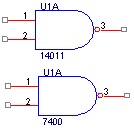

· Hệ thức toán học và Ký hiệu

![]()

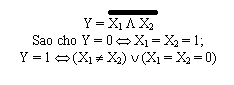

Khi phối hợp Ngõ ra của Mạch Và với một Mạch Đảo sẽ trở thành Mạch Và Đảo (NAND) theo ký hiệu và hệ thức toán học dưới đây:

Khi phối hợp Ngõ ra của Mạch Và với một Mạch Đảo sẽ trở thành Mạch Và Đảo (NAND) theo ký hiệu và hệ thức toán học dưới đây:

Có nghĩa là nếu khi cả hai Ngõ vào đều bằng 1 thì Ngõ ra Y sẽ bằng 0.

Nếu một trong hai Ngõ vào bằng 0 hoặc cả hai Ngõ vào đều bằng 0 thì Ngõ ra sẽ bằng 1.

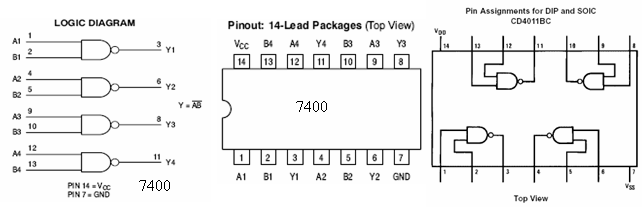

· Các Vi mạch Cơ bản

Có hai loại IC rất thông dụng và gần giống nhau về cấu trúc tức là trong mỗi IC đều chứa 4 Mạch Và Đảo nhưng khác nhau về thứ tự của các Chân đó là 4011 thuộc họ 4xxx và 7400 thuộc họ 74xx.

Hình bên trái và hình ở giữa mô tả cấu trúc và thứ tự chân của 7400, hình bên trái mô tả cấu trúc và thứ tự chân của 4011.

· Ứng dụng

Mạch tạo Dao độngỨng dụng đơn giản nhất của Mạch Và Đảo là dùng để tạo Mạch Dao động có Điều khiển như dưới đây:

Hình trên đây là Mạch Dao động được tạo bởi 1 phần tử Đảo (Not) và một phần tử Và Đảo (NAND) theo kiểu phối hợp RC (gồm R1R2C) được gọi là RC Oscillator: Khi Cổng Reset bằng 0 thì Ngõ ra của phần tử Đảo của Ngõ Reset sẽ được đặt ở mức 1 cho phép phần tử Và Đảo hoạt động và vì thế mạch sẽ dao động được. Ngược lại, nếu Cổng Reset bị đặt lên cao thì Mạch Dao động sẽ bị khoá không thể tạo ra dao động được.

Đối với Mạch Dao động tiếp thep trên đây cũng hoạt động tương tự, tuy nhiên Mạch này được tạo dao động là nhờ vào một Thạch anh 32,786 kHz nên được gọi là Mạch Dao động kiểu Thạch anh Crystal Oscillator.

Để giải thích được nguyên lý hoạt động của các Mạch Dao động này, cần xem tiếp ‘Lý thuyết Dao động’ sẽ trình bày và giải thích chi tiết về Nguyên lý của các Mạch Dao động.

o Mạch Khuyếch đại

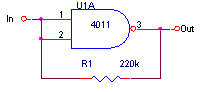

Một số trường hợp cũng sử dụng Mạch Và Đảo với chức năng giống như một Mạch Khuyếch đại đối với những Tín hiệu không quá yếu (không dưới 0,5 V) như được mô tả ở hình dưới đây:

Một số trường hợp cũng sử dụng Mạch Và Đảo với chức năng giống như một Mạch Khuyếch đại đối với những Tín hiệu không quá yếu (không dưới 0,5 V) như được mô tả ở hình dưới đây:

Nếu ghép chung 2 Ngõ vào với nhau, mạch Và Đảo trở thành Mạch Đảo giống như một phần tử Đảo của IC 4069 hoặc 4049 nên nó có thể khuyếch đại được các Tín hiệu không quá bé như Mạch Khuyếcg đại sử dụng phần tử Đảo đã được trình bày ở trên.

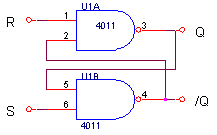

o Mạch Bập bênh (Flip – Flop, viết tắt là Mạch FF)

Mạch Bập bênh FF được thiết lập bởi 2 phần tử Và Đảo như hình bên gồm hai Ngõ vào được gọi là R (được gọi là Reset – Xoá) và S (được gọi là Set – đặt lại). Hai Ngõ ra được gọi là Q (thuận) và /Q (nghịch) tức là đảo nghịch của Q sao cho nếu Q = 1 thì /Q = 0 và ngược lại nếu Q = 0 thì /Q = 1.

Mạch Bập bênh FF được thiết lập bởi 2 phần tử Và Đảo như hình bên gồm hai Ngõ vào được gọi là R (được gọi là Reset – Xoá) và S (được gọi là Set – đặt lại). Hai Ngõ ra được gọi là Q (thuận) và /Q (nghịch) tức là đảo nghịch của Q sao cho nếu Q = 1 thì /Q = 0 và ngược lại nếu Q = 0 thì /Q = 1.

Mạch chỉ hoạt động khi một trong 2 Ngõ vào R hoặc S bị đặt xuống ở mức thấp. Nếu cả 2 Ngõ vào đều ở mức thấp thì được gọi là trạng thái cấm vì lúc này các Ngõ ra không xác định được trạng thái.

Ví dụ, R = 1, S = 0 thì /Q sẽ bằng 1 và Q = 0.

Ngược lại nếu R = 0, S = 1 thì /Q sẽ bằng 0 và Q = 1.

Theo cấu trúc nói trên, bao giờ các Ngõ ra cũng chỉ có một Ngõ được đặt ở mức cao và Ngõ kia bị đặt ở mức thấp (vì 2 Ngõ ra đảo trạng thái với nhau) tức là không bao giờ 2 Ngõ ra có cùng trạng thái vì vậy Mạch nói trên mới được gọi là Mạch Bập bênh (một đầu cao và một đầu thấp giống như một cái Bập bênh).

Nguyên lý của Mạch Bập bênh là chỉ thay đổi trạng thái các Ngõ ra khi và chỉ khi có 1 Ngõ vào bằng 0 và Ngõ vào kia bằng 1, bình thường cả 2 Ngõ vào bằng 1 thì Mạch Bập bênh giữ nguyên trạng thái.

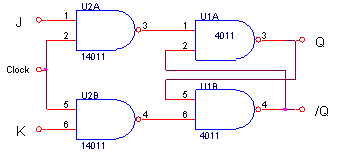

o Mạch Trigger J-K

Hoàn toàn tương tự Mạch FF nói trên, Mạch bên đây được gọi là Mạch Trigger.

Hoàn toàn tương tự Mạch FF nói trên, Mạch bên đây được gọi là Mạch Trigger.

Mạch này chỉ thay đổi trạng thái của các Ngõ ra khi và chỉ khi có Xung điều khiển Clock và một trong hai Ngõ vào J hoặc K bằng 1.

Tức là trạng thái Ngõ vào của mạch này ngược lại so với yêu cầu của Mạch FF và Mạch FF không bị khống chế bới một Lệnh Điều khiển bất kỳ nào còn đối với Mạch Trigger thì bắt buộc phải có Lệnh Điều khiển thì trạng thái các Ngõ ra mới được thay đổi.

o Mạch Chính – Phụ

Bằng cách ghép liên tiếp 2 Mạch Trigger với nhau sẽ tạo thành Mạch Trigger Chính – Phụ và được gọi tắt là Mạch Chính – Phụ như hình dưới đây:

Nếu ghép liên tiếp 2 Trigger J – K sẽ tạo thành Trigger chính – phụ như mô tả trên đây. Trong đó, Trigger đứng trước được gọi là Trigger chính sẽ được mở bằng mức cao H của Xung Clock và Trigger tiếp theo được gọi là Trgger phụ chỉ được mở khi Xung Clock ở mức thấp L.

Nhờ vậy, Trigger chính – phụ hoạt động tương tự một thanh ghi dịch nếu ghép liên tục nhiều phần tử trigger J-K liên tiếp nhau hoặc mỗi Trigger chính – phụ sẽ trở thành một ô nhớ 1 bit.

o Mạch Chia Tần số

Mạch bên đây giới thiệu một Mạch Chia Tần số với những Tần số không vượt quá 2MHz: Nếu Tần số đầu vào là f thì Tần số ở Ngõ ra là f/2 tức có có nghĩa rằng đây là Mạch chia đôi Tần số.

Mạch bên đây giới thiệu một Mạch Chia Tần số với những Tần số không vượt quá 2MHz: Nếu Tần số đầu vào là f thì Tần số ở Ngõ ra là f/2 tức có có nghĩa rằng đây là Mạch chia đôi Tần số.

Mạch hoạt động theo nguyên tắc đơn giản như sau:

Mạch hoạt động dựa trên nguyên tắc của Mạch Bập bênh FF như vừa được trình bày trên đây.

Giả sử phần tử U1A có Ngõ ra là 1 thì theo Nguyên lý Bập bênh bắt buộc Ngõ ra của U1B sẽ phải bằng 0 vì vậy nếu một Tín hiệu vào có Tần số f đặt vào 2 Ngõ vào đồng thời của U1A và U1B thông qua các tụ C1 và C2 thì lúc bấy giờ tương ứng với thời điểm Tín hiệu vào đạt được mức cao (Tín hiệu dao động là Chuỗi Xung vuông ứng với các mức cao và mức thấp luân phiên nhau) thì tại thời điểm đầu tiên vì cả 2 Ngõ vào đều bằng 1 (vì được f đặt vào đồng thời qua tụ C1 và C2) nên tại thời điểm này Mạch sẽ không thay đổi trạng thái của các Ngõ ra so với ban đầu.

Thật vậy, vì Ngõ ra của U1B bằng 1 nên Ngõ vào ở chân số 5 của U1B sẽ bằng 1 vì chân này nối trực tiếp với Ngõ ra của U1A và chân 2 của U1A sẽ bằng 0 vì được nối trực tiếp với Ngõ ra của U1B. Khi đó vì Tín hiệu vào bằng 1 nên cả 2 Ngõ vào của U1B đều bằng 1 nên theo Nguyên lý của Mạch Và Đảo thì Ngõ ra của U1B cũng vẫn bằng 0 như ban đầu và lúc này 2 Ngõ vào của U1A chỉ có một Ngõ vào ở chân 1 do tác động trực tiếp của Tín hiệu vào bằng 1 còn chân 2 bị Ngõ ra của của U1B khống chế nên vẫn bằng 0.

Khi Tín hiệu vào bắt đầu giảm xuống 0 thì vì 1 trong 2 Ngõ vào của U1A đang bằng 0 nên U1A không thay đổi trạng thái nhưng lúc này vì 2 Ngõ vào của U1B đang ở trạng thái đều bằng 1 (do sự tác động của Tín hiệu vào đang ở mức cao chuyển xuống mức thấp) khiến cho 1 Ngõ vào ở chân 6 của U1B bị giảm xuống mức thấp nên theo Nguyên lý của Mạch Và Đảo thì Ngõ ra của U1B sẽ bị đặt lên ở mức cao nghĩa là ngược lại so với trạng thái ban đầu.

Vì Ngõ ra của U1B bị đặt lên mức cao nên nó sẽ tác động vào chân 2 của U1A để khiến cho Ngõ ra của U1A bị lật ngược trạng thái xuống mức 0.

Bằng cách giải thích tương tự, sau khi Tín hiệu vào thay đổi 2 lần từ mức cao xuống mức thấp thì Ngõ ra được thay đổi trạng thái 1 lần tức là Tín hiệu vào tạo ra được 2 xung thì Ngõ ra mới tạo được 1 xung nên mạch nói trên được gọi là Mạch chia đôi Tần số.

Tuy vậy, mạch nói trên hoạt động không tin cậy, nhất là nếu Tần số quá lớn thì mạch nói trên sẽ trở nên ‘bị mù’ vì không thể hoạt động được.

· Thiết kế và lắp ráp

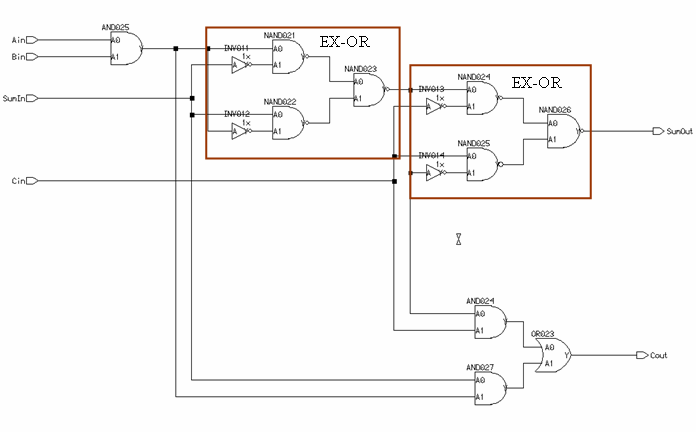

Có thể sử dụng Mạch Và Đảo phối hợp với các phần tử Log khác để thiết kế thành Mạch Toàn Cộng như dưới đây:

Mạch hoạt động như Bảng Sự thật kèm theo: Trong đó X và Y lần lượt là các Bit Số liệu cần được cộng, S (SumOut) là Kết quả phép cộng, C (CarryOut) là Số nhớ của phép cộng. Xem thêm Mạch Bán Cộng và Mạch Toàn Cộng được đề cập thêm ở các phần dưới đây.

· Kiểm tra và phán đoán hư hỏng

Tác giả bài viết: Dr Trần Phúc Ánh

Lưu ý: Các bài viết trên in lại các trang web hoặc các nguồn phương tiện truyền thông khác không xác định nguồn http://tri-heros.net là vi phạm bản quyền

Những tin mới hơn

Những tin cũ hơn

Xem phản hồi

Xem phản hồi Gửi phản hồi

Gửi phản hồi