Thanh ghi 74374

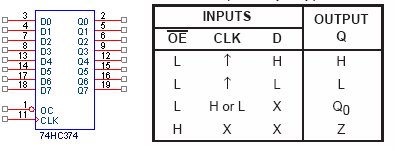

Thứ tư - 23/01/2013 07:42  Ứng dụng nguyên lý Mạch Chốt để chế tạo thành Thanh ghi 74374 là loại Thanh ghi được sử dụng phổ biến nhất ở các Hệ thống Điều khiển. Hình bên đây mô tả cấu trúc, sơ đồ chân và Bảng trạng thái hoạt động của 74374:

Ứng dụng nguyên lý Mạch Chốt để chế tạo thành Thanh ghi 74374 là loại Thanh ghi được sử dụng phổ biến nhất ở các Hệ thống Điều khiển. Hình bên đây mô tả cấu trúc, sơ đồ chân và Bảng trạng thái hoạt động của 74374:

Chân OE (Output Enable) là chân điều khiển cho phép Dữ liệu được xuất ra ngoài tại các Ngõ ra Qn của 74374. Bảng sự thật bên cạnh cho thấy nếu OE = 0 thì các Ngõ ra cho phép xuất Dữ liệu ra. Ngược lại, nếu OE =1 thì các Ngõ ra bị cấm xuất Dữ liệu (các Ngõ ra bị đặt ở trạng thái hở mạch tức là trở kháng cao Z).

Chân CLK là Xung điều khiển cho phép Dữ liệu có thể nhập vào tại các Ngõ vào Dn của 74374. Theo Bảng sự thật cho thấy Dữ liệu vào chỉ được nhập vào 74374 khi Xung CLK đang tăng từ mức thấp L lên mức cao H. Ngược lại nếu Xung CLK ổn định ở mức H hoặc mức L thì Dữ liệu sẽ bị chốt giữ nguyên trạng thái ban đầu không bị thay đổi theo Dữ liệu vào.

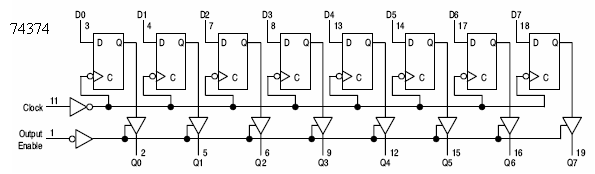

Hình trên mô tả cấu trúc Logic bên trong của Thanh ghi 74374 gồm 8 Trigger Chính – Phụ loại D và các Ngõ ra được chặn trạng thái bởi các Mạch Đệm có điều khiển sao cho khi OE = 1 thì các Ngõ ra bị cấm ở trạng thái hở mạch.

Ứng dụng cơ bản

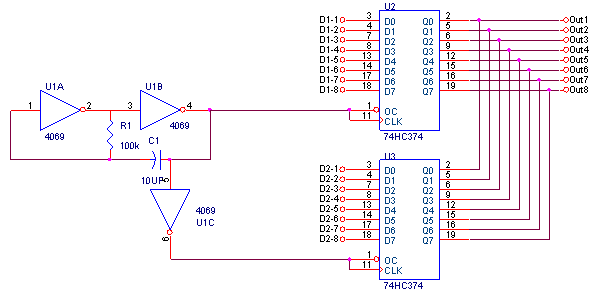

Thanh ghi 74374 được sử dụng phổ biến cho các Hệ thống trao đổi Dữ liệu nhiều cổng Vào/Ra song song như ví dụ đơn giản dưới đây:

Mạch trên đây cho phép nhập Dữ liệu tuần tự từ 2 Cổng vào 8 Bit lần lượt là D1 và D2 sao cho ứng với khi Xung Dao động do Bộ tạo Xung U1A – U1B tạo ra Xung thuận (tức là mức Logic bằng 1) tác động vào Chân điều khiển OC và Clock của U2 thì U2 sẽ nhập được Dữ liệu từ các Ngõ vào D1-1 – D1-8 nhưng vẫn chưa xuất Dữ liệu ra ngoài mà lúc này các Ngõ ra của U2 vẫn đang bị khống chế ở trạng thái Trở kháng cao.

Trong lúc này vì Chân điều khiển OC của U3 bị đảo trạng thái bởi U1C nên Xung tác động lúc này vào Chân điều khiển OC của U3 là ở mức Logic bằng 0 nên U3 được phép xuất Dữ liệu trước đó đã được nhập vào U3 ra ngoài thong qua các Ngõ ra Out1 – Out8.

Khi Xung Dao động của Bộ Dao động U1A – U1B chuyển từ mức cao sang mức thấp thì U2 bắt đầu được phép xuất Dữ liệu ra ngoài đồng thời U3 bị ngắt Ngõ ra vì lúc này Chân OC của U3 nhận Xung đảo thông qua U1C nên mức xung lúc này tác động vào OC của U3 là bằng 1 và cũng vì thể lúc này Xung Clock của UU3 cũng bằng 1 cho phép U3 nhập Dữ liệu từ các Ngõ vào của nó từ D2-1 – D2-8.

Như vậy, U2 và U3 nhập/xuất Dữ liệu theo tuần tự luân phiên nhau…

Tác giả bài viết: Dr Trần Phúc Ánh

Lưu ý: Các bài viết trên in lại các trang web hoặc các nguồn phương tiện truyền thông khác không xác định nguồn http://tri-heros.net là vi phạm bản quyền

Những tin mới hơn

Những tin cũ hơn

Xem phản hồi

Xem phản hồi Gửi phản hồi

Gửi phản hồi